I am a computer hardware engineering with 5+ years of FPGA/ASIC design and machine learning experience. Currently I am working as a Senior FPGA Engineer at USC Information Sciences Institute. I actively develop for and research the latest Xilinx FPGA architectures (Versal, UltraScale+, Series 7) to provide full-device hardware assurance. I also support ASIC design efforts including SoC IP design, integration and verification. I’ve also worked with embedded systems and have experimented with NVIDIA Jetson, Raspberry Pi, Arduino, and microcontrollers.

I am interested in opportunities to further expand my hardware experience through FPGA/ASIC designs for applications in interactive technologies such as mixed reality, biometrics and robotics.

In my free time I love taking on hobby game development projects, exploring the National Parks, and taking care of my dogs Matcha and Mango!

Computer Engineering, M.S.

- Thesis: FPGA Reservoir Computing Networks for Dynamic Spectrum Sensing

- Recognitions: Bradley Research Fellowship, New Horizon Graduate Scholars Program

Computer Engineering, B.S.

- Relevant Coursework: Low Power VLSI Design, Microprocessor Architecture, Machine Learning, Embedded Systems

- Recognitions: Summa Cum Laude, Chairman’s Award, ECE Senior Design Project Award, Honors College

Senior FPGA Engineer

- Architected and integrated a top-level SoC design using SystemVerilog with JTAG, PLL, SerDes, and custom IP for a homomorphic encryption ASIC. Interfaced memory-mapped control-status registers with AXI4Lite interconnect for external FPGA access.

- Developed comprehensive FPGA test platforms using Vivado and Vitis across Xilinx Versal, UltraScale+, and Series 7 devices to validate functionality of slices, interconnect, and hard IP blocks. C code developed for MicroBlaze to enable run-time testing.

- Developed codebase for automating EDA tool build processes and FPGA debugging using Python and TCL. Maintained codebase using GitLab CI/CD flows, merge requests, and issue tracking.

- Implemented and optimized MobileNet accelerator on Zynq ZCU104 using Xilinx FINN framework, Python, Xilinx HLS, and C. Worked towards energy efficiency and latency improvements for object detection and tracking with the BDD100K dataset.

- Performed functional verification and debugging of NoC-based ASIC architectures using Xcelium and emulations on VCU128.

- Collaborated with interns to bring-up a Synopsys HAPS-100 prototyping platform for emulation of ASIC designs.

- Maintained GitLab Wiki repositories to document workflows, facilitate knowledge sharing, and host project documentation.

- Performed formal equivalence checking using Synopsys Formality on FPGA netlists generated by Synopsys Synplify and Xilinx Vivado.

Graduate Research and Teaching Assistant

- Implemented Zynq-7000 FPGA based interface in Vivado and Verilog for an analog neuromorphic image classifier ASIC. The design leveraged the embedded ARM processor, an external DAC, the internal ADC, and custom AXI IP.

- Developed bare-metal C applications to run on Zynq-7000 ARM processor for reading and writing data to the analog ASIC interface.

- Configured a PetaLinux image and device tree for AXI memory-mapped custom IP addressing from Linux running on the ARM CPU. Created Python scripts to streamline IP configuration and evaluation of the neuromorphic ASIC within the embedded OS.

- Used TCL scripts to automate Vivado's FPGA block design and bitstream generation for reproducibility and continuous integration of the neuromorphic ASIC interface architecture. Maintained a GitHub repository for version control and collaboration.

- Designed a recurrent neural network accelerator IP using C++ and Intel HLS Compiler for the BladeRF software defined radio. Performed verification using ModelSim co-simulation, and implemented a bitstream generated for the on-board Cyclone V FPGA.

- Led and instructed a team of 4 undergraduate students in FPGA machine learning accelerator design. Provided weekly lectures, facilitated technical discussions, and advised undergraduate research projects for 3 semesters.

- Conducted research analyzing firmware and hardware vulnerabilities (CVEs) in the NIST National Vulnerability Database for Colvin Run Networks' supply chain risk assessment tool - Copia.

ASIC Verification Engineer

- Developed and maintained SystemVerilog/UVM testbenches for functional verification of 10+ critical IP cores on production SoCs, including PCI, I2C, UART, and SPI interfaces.

- Created a Perl framework for generating wafer-level and package-level manufacturing test patterns for SerDes and MBIST IP validation on RAD5545 SoCs, ensuring production-quality hardware functionality.

- Collaborated with interns in the development of memory test and repair sequences for SoCs using C++ and JTAG Corelis boundary scan hardware. Used on-chip fuses to enable redundant memory columns and repair memory faults for several devices.

- Presented automated MBIST test insertion methodology research to the Virginia Microelectronics Consortium (VMEC), demonstrating innovation in test automation.

- Served in the onsite Young Professionals and Health & Wellness committees.

Private Tutor

- Private tutor specializing in computer science, computer engineering and programming languages

- Subjects include Verilog, VHDL, Java, Python, C, C++, Swift/Xcode, and Calculus

- Nearly 5 years of experience helping students succeed in technical subjects

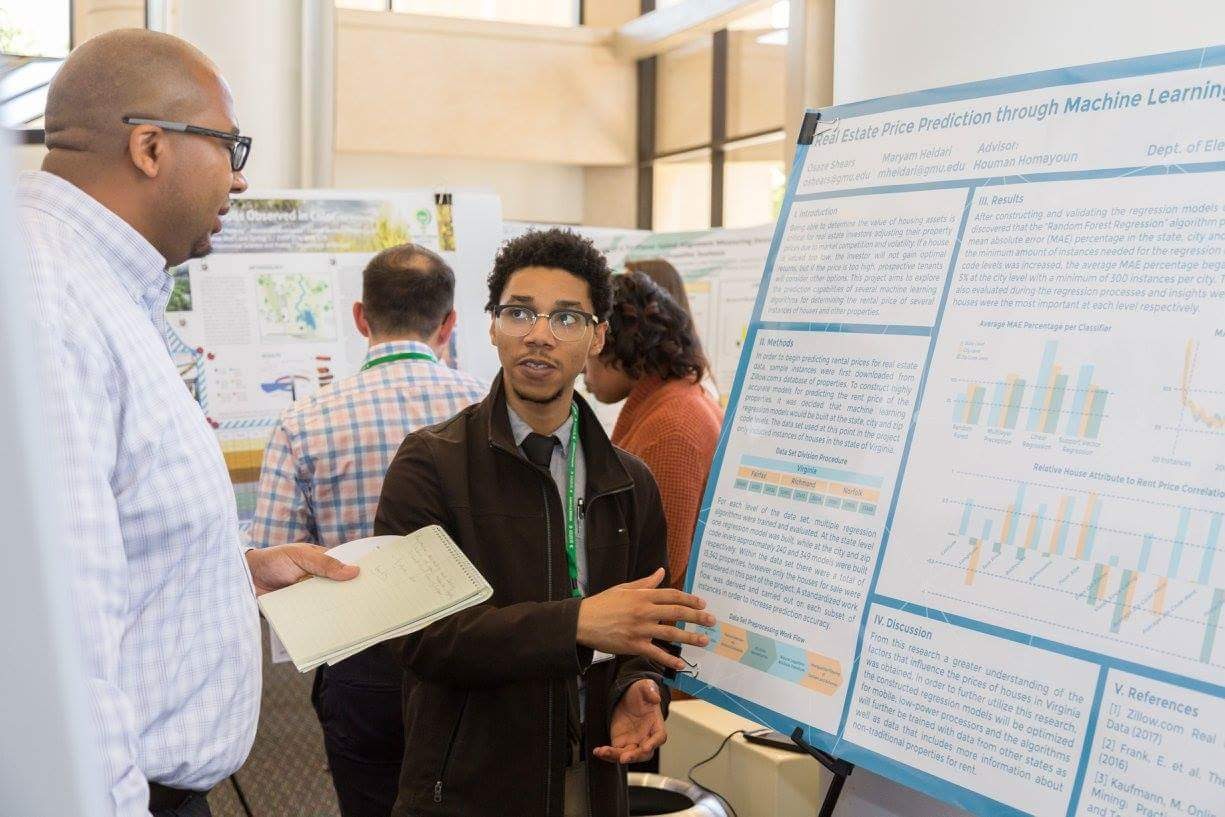

Computer Engineering Undergraduate Researcher

- Learning Assistant (LA) for ECE 331: Digital Systems Design and ECE 332: Digital Electronics and Logic Design Lab

- Peer Mentor for Engineering courses, focusing on Computer Science, Computer Engineering, Physics and Calculus

- Technology Coordinator & STEP Logistics Coordinator for Office of Diversity, Inclusion and Multicultural Education

- President of F1rst Gen Mason student organization

- SystemVerilog/Verilog

- VHDL

- FPGA/ASIC Design

- High-Level Synthesis

- Vivado

- Quartus Prime

- ModelSim

- Questa

- Xcelium

- Synopsys VCS

- Python

- C/C++

- Java

- MATLAB

- UVM

- Git

- GitHub/GitLab

- New Horizons Graduate Scholar

August 2020

Awarded by Virginia Tech's College of Engineering - ECE Department Bradley Fellowship

January 2020

Awarded by Virginia Tech's Electrical and Computer Engineering Department - Summa Cum Laude

May 2018

Awarded by GMU's Volgenau School of Engineering (VSE) - ECE Chairman's Award

May 2018

Awarded by GMU's Electrical and Computer Engineering Department's - ECE Outstanding Academic Achievement Award

May 2018

Awarded by GMU's Electrical and Computer Engineering Department's - ECE Senior Design Project Award

May 2018

Awarded by GMU's Electrical and Computer Engineering Department's for Project LENS - Dean's Advisory Board Award

April 2018

Awarded by GMU's Volgenau School of Engineering (VSE) for Project LENS - Honors College

June 2014 - May 2018

Awarded by GMU's Honors College - OSCAR Fellow

August 2017

Awarded by GMU's Office of Student Scholarship, Creative Activities and Research (OSCAR) - Undergraduate Research Scholar Program (URSP) Grant

January 2017, August 2017

Awarded by GMU's Office of Student Scholarship, Creative Activities and Research (OSCAR) - Black Scholar of the Year

February 2015

Awarded by GMU's Office of Diversity, Inclusion and Multicultural Education (ODIME) - Dean's List

June 2014 - May 2018

Awarded by GMU's Volgenau School of Engineering (VSE)

- Led and instructed a team of 4 undergraduate Virginia Tech students in FPGA machine learning accelerator design. Provided weekly lectures, facilitated technical discussions, and advised undergraduate research projects for 3 semesters.

- Organized New River Valley Game Dev Meetup, fostering networking opportunities and collaboration among local developers.

- Collaborated with domestic and international developers to create multiplayer games in Unity3D for PC and handheld devices.

- Led wellness events for BAE Systems employees including hikes, soccer tournaments, and outdoor excursions.

- Provided tutoring for undergraduate students in programming, digital logic design, and embedded systems courses.