Graduate Research and Teching Assistant

- Implemented Zynq-7000 FPGA based interface in Vivado and Verilog for an analog neuromorphic image classifier ASIC. The design leveraged the embedded ARM processor, an external DAC, the internal ADC, and custom AXI IP.

- Developed bare-metal C applications to run on Zynq-7000 ARM processor for reading and writing data to the analog ASIC interface.

- Configured a PetaLinux image and device tree for AXI memory-mapped custom IP addressing from Linux running on the ARM CPU. Created Python scripts to streamline IP configuration and evaluation of the neuromorphic ASIC within the embedded OS.

- Used TCL scripts to automate Vivado’s FPGA block design and bitstream generation for reproducibility and continuous integration of the neuromorphic ASIC interface architecture. Maintained a GitHub repository for version control and collaboration.

- Designed a recurrent neural network accelerator IP using C++ and Intel HLS Compiler for the BladeRF software defined radio. Performed verification using ModelSim co-simulation, and implemented a bitstream generated for the on-board Cyclone V FPGA.

- Led and instructed a team of 4 undergraduate students in FPGA machine learning accelerator design. Provided weekly lectures, facilitated technical discussions, and advised undergraduate research projects for 3 semesters.

- Conducted research analyzing firmware and hardware vulnerabilities (CVEs) in the NIST National Vulnerability Database for Colvin Run Networks’ supply chain risk assessment tool - Copia.

Summary

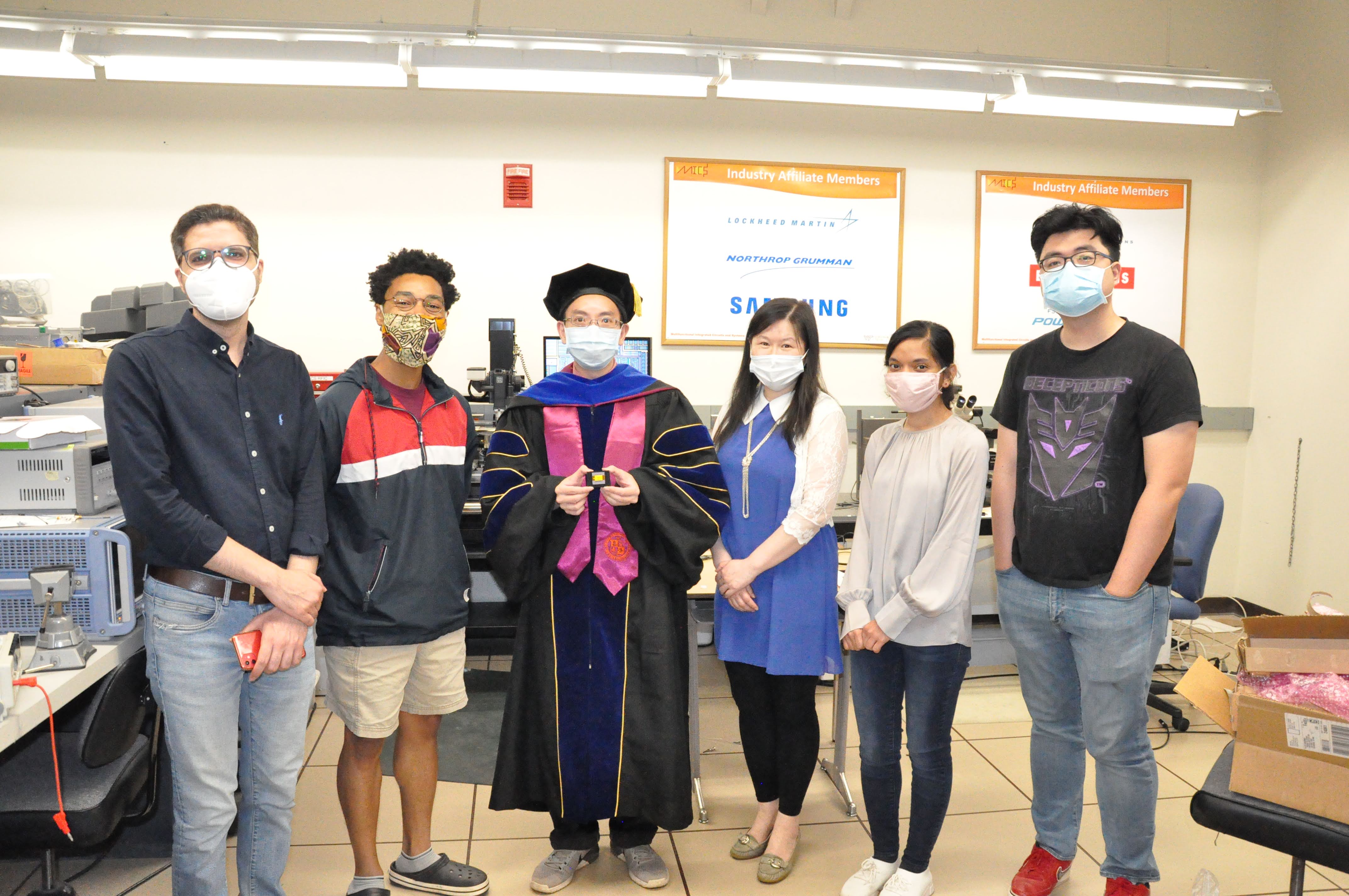

As a Graduate Research Assistant at Virginia Tech’s Electrical and Computer Engineering Department, I conducted research under the Multifunctional Integrated Circuits and Systems (MICS) Lab led by Dr. Yang Cindy Yi. My work focused on studying neuromorphic computing implementations on digital integrated circuits and collaborating with fellow graduate students to develop next-generation machine learning hardware through neuromorphic computing.

Thesis

My M.S. thesis is available to be viewed here: FPGA Reservoir Computing Networks for Dynamic Spectrum Sensing

Publications

Shears, O., Bai, K., Liu, L., & Yi, Y. (2021, November). A hybrid fpga-asic delayed feedback reservoir system to enable spectrum sensing/sharing for low power iot devices iccad special session paper. In 2021 IEEE/ACM International Conference On Computer Aided Design (ICCAD) (pp. 1-9). IEEE.

Teaching Experience

I also served as a Graduate Teaching Assistant (GTA) from August 2020 to May 2021, providing:

- Weekly office hours and remote support for students in ECE 2514: Computational Engineering

- Grading and logistical support for ECE 2514: Computational Engineering

Leadership & Mentoring

During my time at Virginia Tech, I mentored a team of 4 undergraduate students in researching digital neuromorphic computing, machine learning, and reservoir computing, helping to guide the next generation of engineers in this exciting field.

Awards & Recognition

- ECE Department Bradley Fellowship (January 2020) - Awarded by Virginia Tech’s Electrical and Computer Engineering Department