### I. Introduction

The decreasing size of transistors has allowed static random access memory (SRAM) hardware to store an increasing amount of data while retaining its compact size. Although we can store more data than ever before in such a small space, the amount of defects that the hardware is suspect to increases because of manufacturing errors and material inconsistencies. When chips are exposed to these defects, the overall yield for the design is affected.

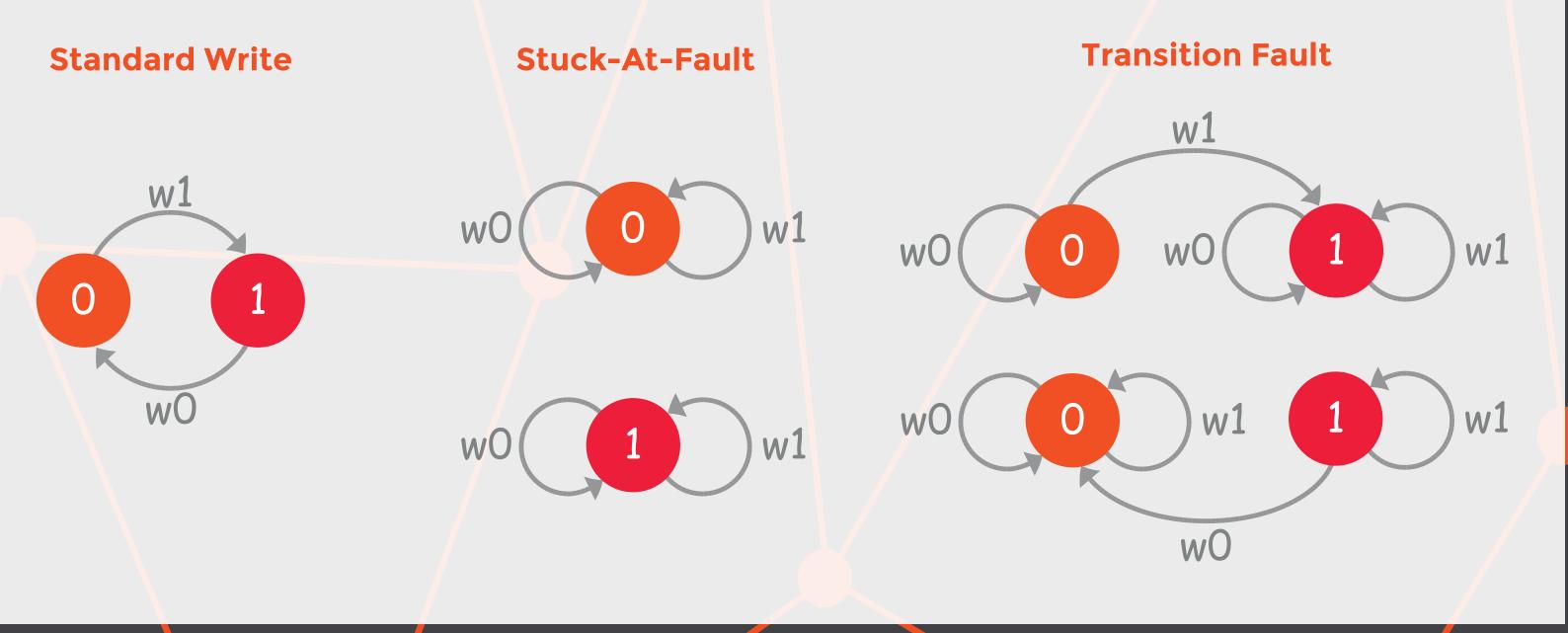

### Memory Defect Finite State Machines

### II. Project Overview

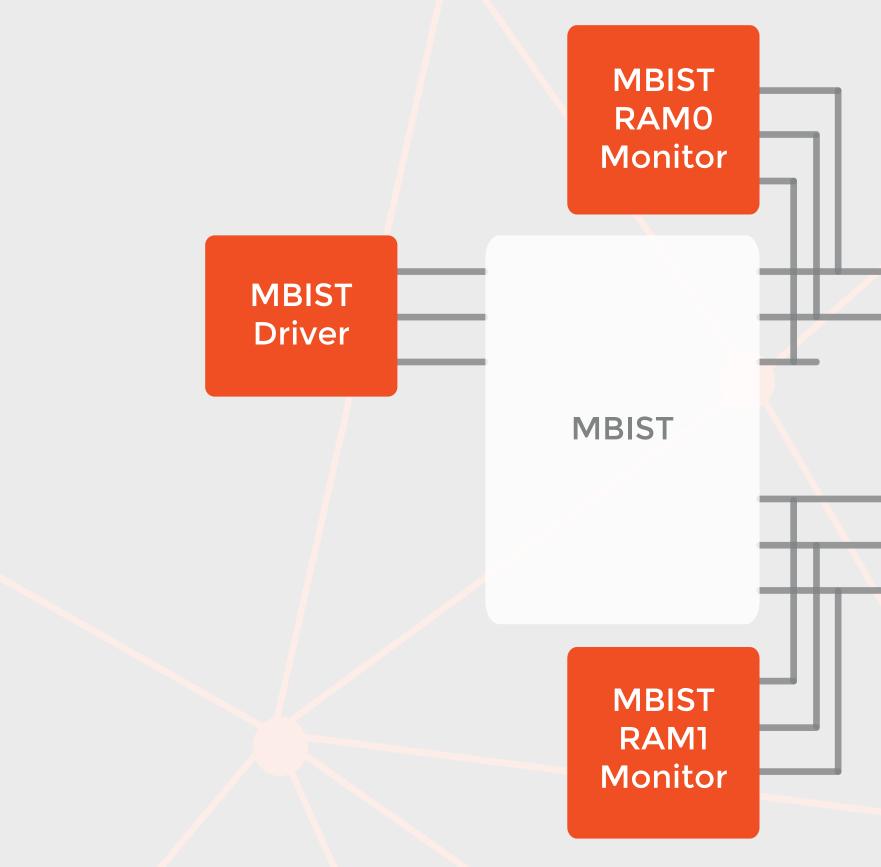

To retain high yield percentages with increasing memory densities, memory built-in self-test (MBIST) hardware has been created for memory test and repair. MBIST hardware can become difficult to integrate into large designs because of the amount of connections required. The following issues have been addressed in this project in an effort to streamline the MBIST integration process.

Verification Issues: Due to the number of port connections between MBIST and each connected memory, ASIC designers may inadvertently wire unrelated ports together. This can cause a design to completely fail future verification.

Automation Issues: When MBIST is not instantiated at the same hierarchical level as memory, ASIC designers must implement several new ports for each hardware component enclosing the memories being tested.

# **Memory Built-In Self Test Integration**

**Osaze Y. Shears - ASIC Hardware Design, BAE Systems Inc., Manassas, Virginia Computer Engineering, George Mason University**

### **V. Experimental Procedure: Automation III. Experimental Procedure: Verification** . Research methods for reducing ports in VHDL & Verilog. **1.** Research all MBIST-to-Memory combinations. 2. Determine which methods are supported by logic synthesis. 2. Create guidance on how to connect MBIST to memories. **3.** Verify all connections were made correctly via test bench. **3.** Use the verification plan from Part 1 to validate connections. **IV. Project Deliverables: Verification VI. Project Deliverables: Automation One Dimensional Vectors Method\* MBIST Connectivity Test Bench** Uses drivers and monitors to evaluate MBIST connections High physical resource utilization and low code overhead Logic-1 (high) bit is driven through all MBIST-memory ports • MBIST data can be easily parsed from the vectors Comparisons made between bits at MBIST and at memory Construct supported in cross-language RTL synthesis **MBIST Verification Plan MBIST Template File Modifications** Covers the process for extracting and simulating test bench Generation software was reconfigured to implement the one and MBIST files from the MBIST generation software dimensional vectors method **Sample MBIST Connectivity Test Bench Failures Logic Signal Concatenation Methods** MBIST Cod **RAMO RAMO** Monitor Monitor Unmodified **1D Vector** MBIST **RAMO** w/ All Ports Driver **1D Vectors** MBIST w/ Similar Ports\* **2D Vector** w/ All Ports RAM1 **2D Vectors** w/ Similar Ports MBIST Interfaces (VL)/ RAM1 RAM1 Records (VHDL) Monitor

## **VII. Future Work**

Further improvements to the outcomes of this project may include:

- Improved physical resource utilization

- Software for inserting MBIST into a design

- Test Bench for simulating several MBIST engines simultaneously

## **VIII. Acknowledgments**

Virginia Microelectronics Consortium (VMEC) for the opportunity to conduct this research and gain an invaluable experience as an ASIC designer. Patty Schaefer and Danny Pirkl, who challenged and guided me as I conducted this work, and introduced me to several leaders within the company. ASIC Hardware Design Team for providing further insights regarding MBIST. Kyle Fowler and John Davis for hosting amazing intern events **BAE Systems employees** that made my internship a great experience.

# **VASON** UNIVERSITY Of Engineering

| le Overhead | Parsing<br>Difficulty | Physical<br>Utilization | Cross-<br>Language |

|-------------|-----------------------|-------------------------|--------------------|

| High        | Low                   | High                    | Yes                |

| Low         | High                  | High                    | Yes                |

| Med         | Med                   | Med                     | Yes                |

| Low         | Low                   | Low                     | Νο                 |

| Med         | Low                   | Med                     | Νο                 |

| Low         | Low                   | High                    | Νο                 |

|             |                       |                         |                    |